권호기사보기

| 기사명 | 저자명 | 페이지 | 원문 | 기사목차 |

|---|

결과 내 검색

동의어 포함

표제지

국문초록

목차

I. 서론 8

1. 연구배경 및 목적 8

1.1. 연구배경 8

1.2. 연구 목적 및 방법 11

II. RFID 시스템의 개요 12

2.1. RFID 시스템 12

2.2. 리더와 태그의 교신 13

2.3. Air Interface 기술 16

2.4. 태그의 전력 공급 17

2.5. RFID Reader와 Tag의 기능 18

2.6. 13.56 MHz 국제 표준 비교 20

2.7. ISO 14443 Type A 21

2.8. ISO 14443 Type B 22

III. 13.56 MHz 수동형 RFID 태그 설계 23

3.1. 13.56MHz RF단 블록도 23

3.2. Rectifier 25

3.3. Demodulator 27

3.4. Regulator 29

3.5. RC Oscillator 31

3.6. Power On Reset 32

3.7. Modulator 34

IV. Simulation과 Layout 및 측정 결과 35

4.1. Rectifier Simulation 결과 35

4.2. Demodulator Simulation 결과 36

4.3. Layout 구현 37

4.4. 측정 결과 38

V. 결론 39

참고문헌 40

Abstract 42

〈그림 1〉 RFID 시스템 구성 12

〈그림 2〉 RF 시스템의 송수신 방식 13

〈그림 3〉 유도성 결합 14

〈그림 4〉 저항성 부하 변조기를 갖는 태그 등가회로 15

〈그림 5〉 리더와 태그의 결합방식 16

〈그림 6〉 ISO 14443 Type A 100% ASK 중지구간 21

〈그림 7〉 ISO 14443 Type A 10% ASK 중지구간 22

〈그림 8〉 13.56㎒ RF단 기능 23

〈그림 9〉 RFID Functional Block Diagram 24

〈그림 10〉 nMOS 게이트 교차연결형 브리지 정류기 25

〈그림 11〉 nMOS 게이트 교차연결형 브리지 정류기 등가회로 26

〈그림 12〉 Demodulator 회로 27

〈그림 13〉 Demodulator 입출력 파형 비교 28

〈그림 14〉 Voltage Regulator 회로 29

〈그림 15〉 RC Oscillator 회로 31

〈그림 16〉 Rower On Reset 회로 32

〈그림 17〉 Modulator 회로 34

〈그림 18〉 Rectifier Simulation 35

〈그림 19〉 비교기를 통해 출력되는 디지털 신호 복원 36

〈그림 20〉 13.56㎒ RFID Analog Front-end Layout 37

〈그림 21〉 데이터 수신과 복원 38

*표시는 필수 입력사항입니다.

| 전화번호 |

|---|

| 기사명 | 저자명 | 페이지 | 원문 | 기사목차 |

|---|

| 번호 | 발행일자 | 권호명 | 제본정보 | 자료실 | 원문 | 신청 페이지 |

|---|

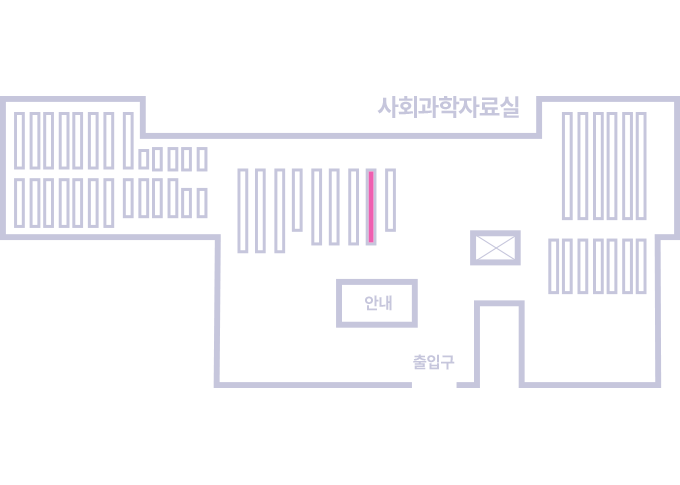

도서위치안내: / 서가번호:

우편복사 목록담기를 완료하였습니다.

*표시는 필수 입력사항입니다.

저장 되었습니다.