권호기사보기

| 기사명 | 저자명 | 페이지 | 원문 | 기사목차 |

|---|

결과 내 검색

동의어 포함

국문목차

표제지=0,1,3

감사의 글=0,4,1

차례=i,5,3

그림차례=iv,8,4

표차례=viii,12,1

국문요약=ix,13,2

제1장. 서론=1,15,2

제2장. 연구 배경=3,17,1

제2-1절. PON 시스템=4,18,3

제2-2절. PON 시스템의 종류=7,21,2

제2-3절. 버스트 모드 클럭/데이터 복원회로의 필요성=9,23,1

제2-4절. 버스트 모드 클럭/데이터 복원회로의 종류=10,24,1

제2-4-1절. gated osciIIator 방식=10,24,3

제2-4-2절. Multi-phase를 이용한 방식=13,27,2

제3장. 622Mbps MO-CDR 회로 설계=15,29,2

제3-1절. 새로운 방식의 클럭 및 데이터 복원 회로=17,31,1

제3-2절. 622Mbps MO-CDR 회로의 동작 및 구현=18,32,3

제3-2-1절. HPSG=21,35,4

제3-2-2절. MO (Muxed Oscillator)=25,39,3

제3-2-3절. 622Mbps MO-CDR 회로의 타이밍도=28,42,4

제3-2-4절. 622Mbps MO-CDR 회로의 특징=32,46,1

제3-3절. 622Mbps MO-CDR 회로의 설계=33,47,1

제3-3-1절. MO의 지연 회로 설계=33,47,4

제3-3-2절. MUX, XOR 설계=37,51,3

제3-4절. 위상 동기 회로=40,54,2

제3-4-1절. 위상 동기 회로의 설계=42,56,9

제3-4-2절. 위상 동기 회로의 시뮬레이션=51,65,2

제3-5절. 데이터 전송 시뮬레이션=53,67,6

제4장. 1.25Gbps MO-CDR 회로 설계=59,73,1

제4-1절. 1.25Gbps MO-CDR 회로의 동작 및 구현=59,73,2

제4-1-1절. HPSG=61,75,3

제4-1-2절. MO=64,78,3

제4-1-3절. 1.25Gbps MO-CDR 회로의 타이밍도=67,81,2

제4-1-4절. 1.25Gbps MO-CDR 회로의 특징=69,83,1

제4-2절. 1.25Gbps MO-CDR회로의 설계=70,84,1

제4-2-1절. MO의 지연 회로 설계=70,84,1

제4-2-2절. MUX, AND 회로 설계=71,85,1

제4-3절. 위상 동기 회로=72,86,1

제4-3-1절. 위상 동기 회로의 설계=72,86,3

제4-3-2절. 위상 동기 회로의 시뮬레이션=75,89,2

제4-4절. 입ㆍ출력 버퍼=77,91,4

제4-5절. 데이터 전송 시뮬레이션=81,95,5

제5장. 측정 결과 및 토의=86,100,1

제5-1절. 칩 테스트 (622Mbps MO-CDR)=86,100,15

제5-2절. 칩 테스트 (1.25Gbps MO-CDR)=101,115,15

제6장. 결론 및 향후 연구=116,130,2

참고문헌=118,132,3

ABSTRACT=121,135,2

jpg

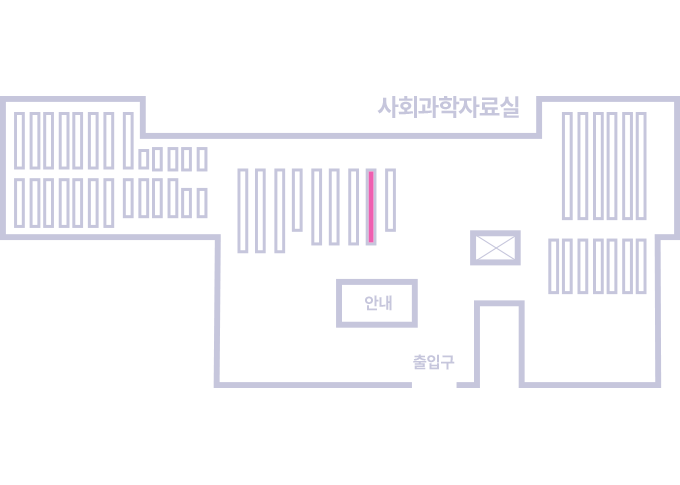

그림4-16 회로의 레이아웃=85,99,1

그림5-1 제작한 칩의 사진=89,103,1

그림5-2 위상 동기 회로 측정을 위한 실험 환경=90,104,1

그림5-3 위상 동기 회로내의 VCO 출력의 지터 특성=91,105,1

그림5-4 데이터 전송 실험을 위한 환경=92,106,1

그림5-6 지터 인가된 400Mbps 입력과 출력의 eye 다이어그램=94,108,1

그림5-7 지터 인가된 622Mbps 입력과 출력의 eye 다이어그램=95,109,3

그림5-10 +25%의 입력 데이터 degradation이 발생했을 경우 복원 데이터 파형=98,112,1

그림5-11 -25%의 입력 데이터 degradation이 발생했을 경우 복원 데이터 파형=99,113,1

그림5-12 제작한 칩의 사진=103,117,1

그림5-13 위상 동기 회로 측정을 위한 실험 환경=104,118,1

그림5-14 위상 동기 회로내의 VCO 출력의 지터 특성=105,119,1

그림5-15 데이터 전송 실험을 위한 환경=106,120,1

그림5-18/5-18 복원 데이터의 eye 다이어그램 ⓐ1Gbps=109,123,1

그림5-19/5-19 복원 데이터의 eye 다이어그램 ⓐ1.25Gbps=110,124,1

*표시는 필수 입력사항입니다.

| 전화번호 |

|---|

| 기사명 | 저자명 | 페이지 | 원문 | 기사목차 |

|---|

| 번호 | 발행일자 | 권호명 | 제본정보 | 자료실 | 원문 | 신청 페이지 |

|---|

도서위치안내: / 서가번호:

우편복사 목록담기를 완료하였습니다.

*표시는 필수 입력사항입니다.

저장 되었습니다.