권호기사보기

| 기사명 | 저자명 | 페이지 | 원문 | 기사목차 |

|---|

결과 내 검색

동의어 포함

표제지

목차

제 1장 서론 2

제 2 장 전력 증폭기 4

2.1 전력 증폭기의 기본이론 4

2.1.1 상호 컨덕턴스( ) 6

2.2 전력 증폭기의 분류 8

2.2.1 CLASS A 전력 증폭기 8

2.2.2 CLASS B 전력 증폭기 13

2.2.3 CLASS AB 전력 증폭기 14

2.2.4 CLASS C 전력 증폭기 16

2.3 Transconductance time delay 18

2.4 Gate-Source Capacitance 18

2.5 Channel Resistance 19

제 3 장 Load-pull 과 Load Line 22

3.1 Loda-pull 측정 방법 22

3.2 Load-pull 방법을 이용한 전력 정합 24

3.3 Load Line Approach 27

3.3.1 Load Line 30

제 4 장 Hot S22 37

4.1 Hot S22 및 Hot S22 측정의 유용한 경우 37

4.2 다른 Hot S 파라메타 와 안정도(K-factor) 39

제 5 장 실험 및 결과 고찰 47

5.1 Hot S22 실험 48

5.2 안정도(K-factor) 시뮬레이션 51

5.3 측정의 제약 53

5.4 교정과 불확실성 57

제 6 장 결론 58

참고문헌 59

Abstract 62

그림 2-1 FET의 등가 회로 6

그림 2-2 Vgs 에 따른 의 변화 7

그림 2-3 Gate Voltage 에 대한 IDS (Drain - Source Current) 의 곡선 8

그림 2-4 전력 증폭기에서 RF 신호의 Gate단 인가 10

그림 2-5 Gate단 전압 변화에 따른 VDS 변화 10

그림 2-6 입력 파워의 과잉으로 인한 cutoff와 포화 상태에서의 clipped 파형 12

그림 2-7 최대 작동을 위한 이상적인 Bias point 13

그림 2-8 Class AB에서의 동작점 설명 16

그림 2-9 Class C 에서의 동작점 설명 17

그림.2-10 Gate-Drain 전압에 의한 Effective gate length와 delay 18

그림 2-11 Vgs와 Vds간의 gm 곡선 19

그림 2-12 Vgs와 Rds간의 Vds 곡선 20

그림 2-13 주파수에 따른 Rds의 변화 21

그림 3-1 간략한 load-pull 구성 23

그림 3-2 BJT 트랜지스터의 입출력 임피던스 25

그림 3-3 BJT 트랜지스터의 입출력 임피던스 변화 25

그림 3-4 임피던스 변화에 대한 S22 변화. (임피던스 :7-j3) 26

그림 3- 5 트랜지스터의 최대 출력점 26

그림 3-6 임피던스 변화에 대한 S22 와 P1dB 변화.(임피던스=4+j0) 27

그림 3-7 시간함수를 이용한 전압과 전류의 관계 28

그림 3-8 Ids 와 Vds 에 대한 Optimum Load Line 30

그림 3-9 Class A에서의 Load impedance 와 Optimum Load Line의 관계 31

그림. 3-10 시간에 따른 전압과 전류의 변화 32

그림. 3-11 시간에 따른 전압과 전류의 변화 32

그림 3-12 Load 임피던스와 Optimum Loda 임피던스가 matching 되었을때의 출력 파워와 Linearity 33

그림 3-13 간단한 정합 회로 구성 34

그림 3-14 트랜스포머를 이용한 매칭 회로 구성 34

그림 3-15 Lumped 소자를 이용한 정합 회로 35

그림 3-16 Ids와 Vds간의 Load Line의 변화 35

그림 3-17 Load Line 변화에 대한 Output matching 회로 36

그림 4-1 간략한 Hot S22 측정 블록도 37

그림 4-2 안정도 향상을 위한 Negative feedback 42

그림 4-3 ATF-34143의 안정도.Fig. 4-3 Stability circle of ATF-34143 43

그림 4-4 Feedback 회로를 이용한 안정도 44

그림 4-5 안정도 향상을 위한 resistive loading의 네가지 형태 45

그림 4-6 ATF-35143의 안정도 46

그림 4-7 직렬 feedback 저항을 사용한 안정도 47

그림 5-1 네트웍 어널 라이저를 사용한 Hot S22 측정 예 48

그림 5-2 소신호, 적당한 압축 상태(0.5dB 미만으로 압축)에서 증폭기의 Hot S22 측정의 예. 49

그림 5-3 매우 낮은 입력 전력과 ~25dBm 출력 전력을 얻기 위한 레벨에서 1W 증폭기의 Hot S22 측정 50

그림 5-4 전력 증폭기에서의 일반적인 S22와 Hot S22 51

그림 5-5 3단 증폭기의 시뮬레이션 52

그림 5-6 증폭기의 시퓰레이션 결과 53

그림 5-7 Hot S22 측정 시험 세트 구성(모든 컴포넌트 + PATS 시험 세트) 57

*표시는 필수 입력사항입니다.

| 전화번호 |

|---|

| 기사명 | 저자명 | 페이지 | 원문 | 기사목차 |

|---|

| 번호 | 발행일자 | 권호명 | 제본정보 | 자료실 | 원문 | 신청 페이지 |

|---|

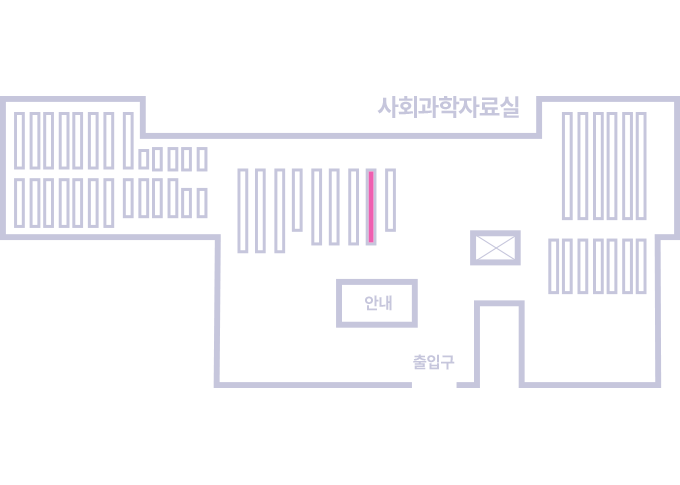

도서위치안내: / 서가번호:

우편복사 목록담기를 완료하였습니다.

*표시는 필수 입력사항입니다.

저장 되었습니다.