권호기사보기

| 기사명 | 저자명 | 페이지 | 원문 | 기사목차 |

|---|

결과 내 검색

동의어 포함

목차

제 1 장 서론 8

제 2 장 컨볼루셔널 코드(Convolutional Codes) 10

제 1 절 컨볼루셔널 코드 부호기 10

제 2 절 비터비 알고리즘(Viterbi Algorithm) 13

제 3 장 터보 코드(Turbo Codes) 17

제 1 절 터보 코드 부호기 17

제 2 절 터보 코드 복호기 20

제 4 장 TMS320C6701 DSP Processor 31

제 1 절 TMS320C6701의 특징 및 구성 32

제 2 절 TMS320C6701 프로그램의 최적화 36

제 3 절 호스트 프로그램과 타갯 프로그램 39

제 5 장 시스템 구성 및 구현 결과 43

제 1 절 시스템 구성 43

제 2 절 시스템 구현 결과 46

제 6 장 결론 54

참고문헌 55

ABSTRACT 57

[그림 1] 컨볼루셔널 코드 부호기(K=3, R=1/3) 11

[그림 2] K=9, R=1/3인 컨볼루셔널 코드 부호기(IS-95 역방향링크) 12

[그림 3] 비터비 복호기의 블록도 14

[그림 4] 터보 코드 부호기(구속장 K=3) 18

[그림 5] 터보 코드의 복호기 구조 21

[그림 6] 복호 과정에서의 소프트 입출력 복호기 22

[그림 7] 순방향 상태 메트릭 25

[그림 8] 역방향 상태 메트릭 26

[그림 9] SOVA 복호기의 구조 29

[그림 10] TMS320C6701 블록 다이어그램 34

[그림 11] TMS320C6701 소프트웨어 개발 흐름도 36

[그림 12] DSP 보드에서 사용되는 프로그램의 전반적인 구조 42

[그림 13] TMS320C6701 보드 실제 모습 45

[그림 14] 실제 보드 시스템 구성 모습 45

[그림 15] 비터비 알고리즘을 이용한 컨볼루셔널 코드의 복호성능 47

[그림 16] 복호성능 BER (log-MAP, 400bits/frame, 반복복호 5회) 48

[그림 17] 복호성능 FER (log-MAP, 400bits/frame, 반복복호 5회) 48

[그림 18] 복호성능 BER (log-MAP, 800bits/frame, 반복복호 5회) 49

[그림 19] 복호성능 FER (log-MAP, 800bits/frame, 반복복호 5회) 49

[그림 20] 복호성능 BER (log-MAP, 1600bits/frame, 반복복호 5회) 50

[그림 21] 복호성능 FER (log-MAP, 1600bits/frame, 반복복호 5회) 50

[그림 22] 복호성능 BER (SOVA, 400bits/frame, 반복복호 5회) 51

[그림 23] 복호성능 FER (SOVA, 400bits/frame, 반복복호 5회) 51

[그림 24] 복호성능 BER (SOVA, 800bits/frame, 반복복호 5회) 52

[그림 25] 복호성능 FER (SOVA, 800bits/frame, 반복복호 5회) 52

[그림 26] 복호성능 BER (SOVA, 1600bits/frame, 반복복호 5회) 53

[그림 27] 복호성능 FER (SOVA, 1600bits/frame, 반복복호 5회) 53

*표시는 필수 입력사항입니다.

| 전화번호 |

|---|

| 기사명 | 저자명 | 페이지 | 원문 | 기사목차 |

|---|

| 번호 | 발행일자 | 권호명 | 제본정보 | 자료실 | 원문 | 신청 페이지 |

|---|

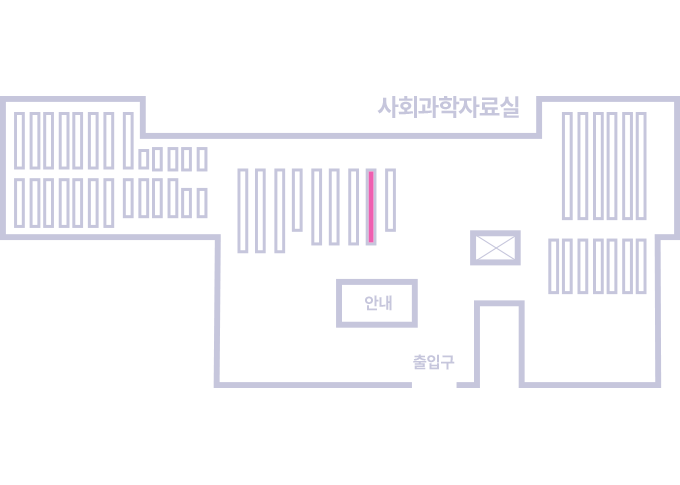

도서위치안내: / 서가번호:

우편복사 목록담기를 완료하였습니다.

*표시는 필수 입력사항입니다.

저장 되었습니다.