권호기사보기

| 기사명 | 저자명 | 페이지 | 원문 | 기사목차 |

|---|

결과 내 검색

동의어 포함

표제지

ABSTRACT

목차

제I장 서론 16

1. 연구 배경 및 연구의 필요성 16

2. 논문 구성 22

제II장 폴딩-인터폴레이팅 아날로그/디지털 변환기 24

1. 일반적인 폴딩-인터폴레이팅 A/D 변환기 26

1.1. 폴딩 A/D 변환기의 기본 구조 및 원리 26

1.2. 인터폴레이팅(Interpolating) 기법 29

1.3. 해상도에 따른 폴딩 파라미터 정의 32

1.4. 폴딩 A/D 변환기의 문제점 33

2. 종속형 (Cascaded) 폴딩-인터폴레이팅 A/D 변환기 35

2.1. 종속형 폴딩-인터폴레이팅 A/D 변환기의 구조 및 동작 원리 35

2.2. 종속형 폴딩-인터폴레이팅 A/D 변환기의 장단점 36

3. 폴딩-인터폴레이팅 A/D 변환기 칩 설계의 최근 동향 38

제III장 새로운 종속형 폴딩-인터폴레이팅 아날로그/디지털 변환기의 개요 42

1. 기존의 종속형 폴딩-인터폴레이팅 A/D 변환기의 문제점 42

2. 새로운 폴딩-인터폴레이팅 A/D 변환기의 특징과 동작원리 44

제 IV장 기본 구성 회로설계의 실제 49

1. 입력단-T/H(Track and Hold Circuit) 49

2. 초단 증폭기 (Preamplifier) 52

3. 옵셋 보정(Resistor Averaging Network)과 인터폴레이션 기법 54

4. 폴딩 증폭기(Foding Amplifiers/Folder) 59

5. 비교기(Comparators) 63

6. 디지털 인코더(Digital Encoder) 66

6.1. 새로운 디지털 인코더의 구조 66

6.2. 버블 에러 보정과 차동 논리 회로 66

제V장 폴딩-인터폴레이팅 아날로그/디지털 변환기 회로의 시뮬레이션 및 칩 레이아웃 70

1. 200 MS/s 급 A/D 변환기 칩의 사양 70

2. 모의 실험 결과 71

3. 제작된 칩의 레이아웃 및 현미경 사진 75

제VI장 아날로그/디지털 변환기의 보드 테스트 셋업 77

1. 상용 아날로그/디지털 변환기를 이용한 기본 성능 테스트 79

1.1. 100 MS/s급 A/D 변환 모듈 설계 79

1.2. 200 MS/s급 A/D 변환 모듈 설계 89

2. IEEE Std. 1241-2000 에 의한 아날로그/디지털 변환기 성능 테스트 100

2.1. A/D 변환기의 정적 특성 및 동적 특성 101

2.2. A/D 변환기의 측정 방법 102

2.3. A/D 변환기 측정을 위한 PCB 설계 기법 105

제VII장 측정 결과 109

제VIII장 결론 114

참고 문헌 116

이력서 124

그림 1.1. A/D 변환기의 응용 분야 17

그림 1.2. 최근 A/D 변환기 개발 동향 22

그림 2.1. (a) 폴딩 A/D 변환기 기본 구조 (b) 입출력 특성 27

그림 2.2. 폴딩 회로 27

그림 2.3. 폴딩 신호 28

그림 2.4. 8비트 폴딩 A/D 변환기 30

그림 2.5. 인터폴레이팅 기법에 의한 폴딩 신호의 생성 31

그림 2.6. Cascaded 폴딩-인터폴레이팅 A/D 변환기 구조 36

그림 3.1. 제안하는 Cascaded 폴딩-인터폴레이팅 A/D 변환기의 구조 45

그림 3.2. Averaging 효과 (DNL) 46

그림 3.3. Averaging 효과 (INL) 46

그림 4.1. 입력단의 등가 모델 50

그림 4.2. 입력단과 T/H 회로의 동적 특성 51

그림 4.3. 초단 증폭기(preamplifier) 의 회로도 53

그림 4.4. 저항열을 이용한 평준화 및 인터폴레이팅 기법 55

그림 4.5. 저항열을 이용한 평준화 및 인터폴레이팅 기법(상세) 56

그림 4.6. resistive offset averaging network 57

그림 4.7. 초단 증폭기의 전달 특성 58

그림 4.8. 기존의 폴딩 증폭기 회로 59

그림 4.9. 개선된 폴딩 증폭기 회로 (공통 모드) 60

그림 4.10. 개선된 폴딩 증폭기 회로 (차동 모드) 61

그림 4.11. 비교기 회로도 64

그림 4.12. 비교기의 시뮬레이션 파형 65

그림 4.13. 새로운 디지털 인코더의 구조 67

그림 4.14. 버블 에러 보정 (Voting process) 68

그림 4.15. Voting 회로 (DCVSPG) 69

그림 5.1. folding 신호 파형 71

그림 5.2. 각 폴딩단에서의 신호 파형 72

그림 5.3. 디지털 인코더의 응답 특성 73

그림 5.4. 디지털 인코더의 응답 특성 (비교) 73

그림 5.5. 램프 입력 특성 74

그림 5.6. DNL 시뮬레이션 결과 74

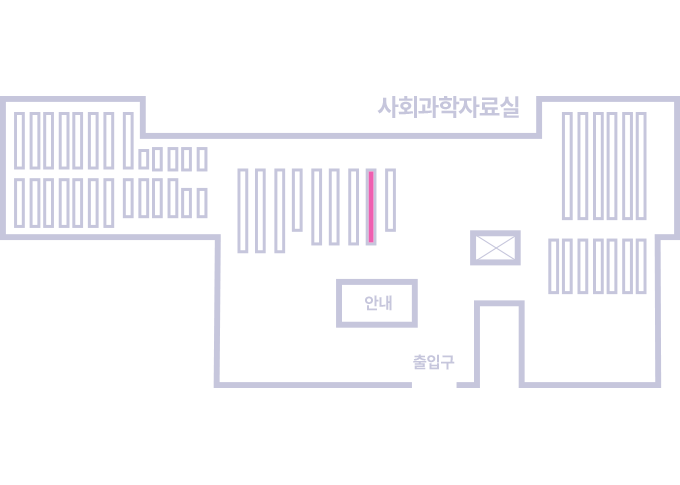

그림 5.7. 칩의 floor plan 75

그림 5.8. 제작된 칩의 현미경 사진 76

그림 6.1. 100MS/s급 A/D 변환 모듈 (1차) 81

그림 6.2. 100MS/s급 A/D 변환 모듈 (2차) 82

그림 6.3. 주요 신호의 타이밍도 83

그림 6.4. 제작된 100MS/s A/D 변환 모듈 사진 84

그림 6.5. 100MS/s A/D 변환 모듈 테스트 셋업 84

그림 6.6. 모듈 테스트 환경 85

그림 6.7. 측정된 A/D 변환 모듈의 DNL 특성 86

그림 6.8. Ramp 신호 복원 파형 87

그림 6.9. 정현파 복원 파형 87

그림 6.10. Ramp 신호 복원 파형 (5MHz) 88

그림 6.11. 정현파 신호 복원 파형 (5MHz) 88

그림 6.12. 200MS/s급 A/D 변환 모듈 구조 92

그림 6.13. 주요 신호의 타이밍도 (200MS/s) 93

그림 6.14. 주요 컨트롤 신호 94

그림 6.15. 데이터 타이밍도 (Odd Bank) 95

그림 6.16. 데이터 타이밍도 (Even Bank) 95

그림 6.17. FIFO를 이용한 200MS/s급 A/D 변환 모듈 구조 97

그림 6.18. 정현파 신호 복원 결과 (200MS/s) 98

그림 6.19. 200MS/s A/D 변환 모듈의 주파수 특성 99

그림 6.20. 제작된 200 MS/s급 A/D 변환 모듈 사진 99

그림 6.21. 정현파 입력을 위한 셋업 103

그림 6.22. 임의 파형 입력을 위한 셋업 103

그림 6.23. 스텝 혹은 펄스 입력을 위한 셋업 103

그림 7.1. DNL/INL 측정 파형 110

그림 7.2. 입력 신호 주파수에 따른 SFDR 111

그림 7.3. 주파수 응답 특성 111

그림 7.4. Reconstructed Beat Sinewave 112

As the demands for high-speed embedded analog-to-digital converter (ADC) are increasing, the small chip area and the low power consumption as well as the fast conversion rate are essential requirements in ADC design. Folding/interpolating ADCs with a time-continuous two-step nature can be implemented with relatively low power consumption and small chip area while maintaining the fast conversion rate of flash architecture.

In this thesis, an 8-bit 200MS/s CMOS 2-stage cascaded folding/interpolating ADC chip was implemented by applying a resistor averaging/interpolating scheme at the preamplifier outputs and the differential circuits for the encoder logic block, with a 0.35-㎛ double-poly CMOS process. The number of preamplifiers was reduced to half, by using an averaging technique with a resistor array at the preamplifier outputs. The delay time of digital encoder block was reduced from 2.2ns to 1.3ns by replacing the standard CMOS logic with DCVSPG and CPL differential circuits. The measured SFDR was 42.5dB at the sampling rate of 200MS/s for the 10.072MHz sinusoidal input signal.*표시는 필수 입력사항입니다.

| 전화번호 |

|---|

| 기사명 | 저자명 | 페이지 | 원문 | 기사목차 |

|---|

| 번호 | 발행일자 | 권호명 | 제본정보 | 자료실 | 원문 | 신청 페이지 |

|---|

도서위치안내: / 서가번호:

우편복사 목록담기를 완료하였습니다.

*표시는 필수 입력사항입니다.

저장 되었습니다.