권호기사보기

| 기사명 | 저자명 | 페이지 | 원문 | 기사목차 |

|---|

결과 내 검색

동의어 포함

In this paper, design methodologies suitable for implementing digital systems at various processes are suggested. Important issues such as Multi Corner Multi Mode, Hierarchical Design, adoption of CCS model, and changes in design flow must be considered for ultra-fine processes. The Cortex-M0 SoC Platform is implemented, taking into account theses important issues, and the results using various digital libraries are compared.

All implemented platforms meet specifications and operate normally with both hardware and software. The fastest clock cycle that can be synthesized is 4ns for Samsung 28nm process.*표시는 필수 입력사항입니다.

| 전화번호 |

|---|

| 기사명 | 저자명 | 페이지 | 원문 | 기사목차 |

|---|

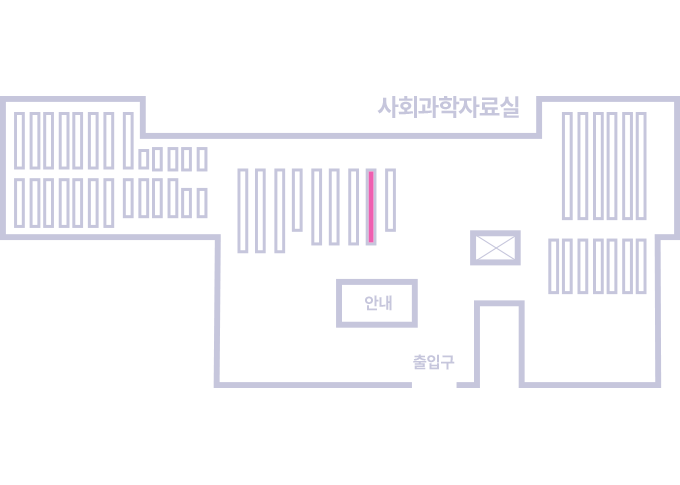

| 번호 | 발행일자 | 권호명 | 제본정보 | 자료실 | 원문 | 신청 페이지 |

|---|

도서위치안내: / 서가번호:

우편복사 목록담기를 완료하였습니다.

*표시는 필수 입력사항입니다.

저장 되었습니다.