권호기사보기

| 기사명 | 저자명 | 페이지 | 원문 | 기사목차 |

|---|

결과 내 검색

동의어 포함

표제지

목차

국문초록 10

제1장 서론 12

1.1. Neuromorphic 12

1.2. Flash Memory 배경 15

1.3. Neuromorphic에 대한 연구 동향 16

제2장 실험 방법 18

2.1. 시냅스 소자 제작 18

2.2. 금속 게이트 Pt, Cr 두께 측정 실험 23

2.3. Floating Gate 3 μm x 3 μm Array 실험 26

2.4. 제작된 소자의 동작 원리 29

제3장 실험 결과 및 토의 33

3.1. 절연막 두께 및 절연 특성 및 소자 조건 확립 33

3.1.1. Tunnel Oxide 조건 확립 33

3.1.2. Control Oxide 최적화 조건 확립 38

3.1.3. 제작된 전체 소자 45

3.1.4. Reading Voltage 결정 48

3.2. 인공 시냅스 소자의 시냅스 가중치 50

3.3. 인공 시냅스 소자의 신뢰성 56

3.3.1. 소자 내구성 56

3.3.2. 소자 보존성 개선 실험 59

3.4. Floating Gate 3 μm x 3 μm Array 결과 63

제4장 결론 67

참고문헌 69

영문초록 74

학회 발표 및 연구 논문 실적 76

[그림. 1] 인공 시냅스 소자 공정도 21

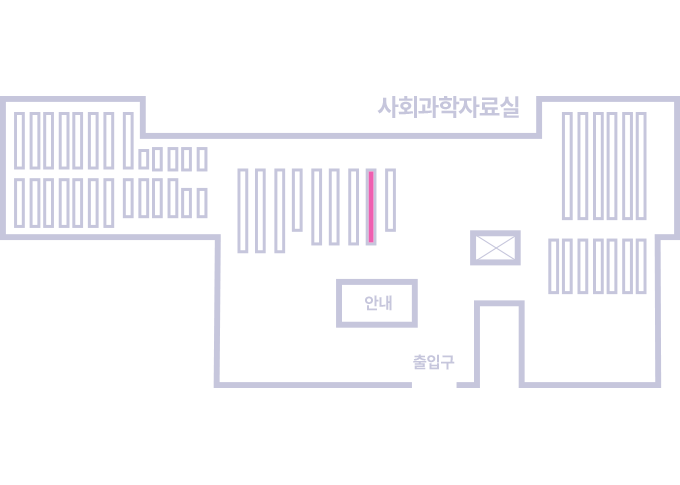

[그림. 2] 50 μm x 50 μm FG, 제작된 소자의 평면도 22

[그림. 3] 인공 시냅스 소자의 단면도 및 Capacitance-Voltage, Current-Voltage Sweep 측정 22

[그림. 4] Pt 증착 50 W에서 20 분간 진행 후 소자의 AFM 단차 측정결과 24

[그림. 5] Cr 증착 50 W에서 20 분간 진행 후 소자의 AFM 단차 측정결과 25

[그림. 6] 3 μm x 3 μm Array FG 정면도, 제작된 전체 소자 28

[그림. 7] 인가전압 Vg에 따른 소자 내 전자들의 움직임[이미지참조] 30

[그림. 8] Flat band Voltage condition의 밴드 다이어그램 (a), Vg ≫ VT > 0일때, 밴드 다이어그램 (b), Vg ≪ 0일때, 밴드 다이어그램 (c)[이미지참조] 32

[그림. 9] Tunnel Oxide 특성 측정을 위한 소자 단면도 34

[그림. 10] Tunnel Oxide의 Capacitance-Voltage 특성 곡선 35

[그림. 11] Tunnel Oxide의 Current-Voltage 특성 곡선 37

[그림. 12] F-N Tunneling와 Direct Tunneling 식 [3],식 [4]에 적용한 그래프 37

[그림. 13] Control Oxide 특성 측정을 위한 소자 단면도 38

[그림. 14] Control Oxide HfO₂ 100 cycles (a), (b), HfO₂ 150 cycles (c), (d), HfO₂ 200 cycles (e), (f) Capacitance-Voltage, Current-Voltage 특성 곡선 43

[그림. 15] Pt/Cr/HfO₂/Si의 구조로 HfO₂ 200 cycles 측정된 Capacitance-Voltage 44

[그림. 16] 제작된 전체 소자의 단면도 45

[그림. 17] Pt/Cr/HfO₂/Pt/Cr/HfO₂/SiO₂/Si의 적층구조로 제작된 전체 소자의 Capacitance-Voltage 특성 곡선, VT < 0.8[이미지참조] 46

[그림. 18] Pt/Cr/HfO₂/Pt/Cr/HfO₂/SiO₂/Si의 적층구조로 제작된 전체 소자의 Current-Voltage 특성 곡선 47

[그림. 19] 소자 상태 측정의 Reading Voltage에 해당하는 Capacitance-Voltage 49

[그림. 20] Program voltage 7 V 1 초 (a), erase voltage -5.8 V 1 초(b)의 인가전압을 반복적 형태로 나타낸 Capacitance-Voltage 52

[그림. 21] Program voltage 7 V 1 초 erase voltage -5.8 V 1 초 반복 인가를 Vref 형태로 나타낸 시냅스 가중치[이미지참조] 53

[그림. 22] Program voltage 7 V 1 초 (a), erase voltage -6 V 1 초 (b)의 형태로 나타낸 Capacitance-Voltage 54

[그림. 23] Program voltage 7 V 1 초 erase voltage -6 V 1 초 반복 인가를 Vref 형태로 나타낸 시냅스 가중치[이미지참조] 55

[그림. 24] Program 7 V 및 erase -5.8 V 145 회 반복하여 Vref 형태로 나타낸 소자 내구성[이미지참조] 58

[그림. 25] Program 7 V 및 erase -6 V 181 회 반복하여 Vref 형태로 나타낸 소자 내구성[이미지참조] 58

[그림. 26] Pt/Cr/HfO₂/Pt/Cr/HfO₂/SiO₂/Si 소자 program 전자 보존성 60

[그림. 27] Photo Resist passivation 층 단면도 (a), SiO₂ passivation 층 단면도 (b) 61

[그림. 28] PR passivation program 및 erase 전자 보존성 61

[그림. 29] Photo Resist passivation 층 program 이후 2 시간 동안의 전하 보존성 (a), SiO₂ passivation 층 program 이후 2 시간 동안의 전하 보존성 (b) 62

[그림. 30] Tunnel Oxide Current-Voltage 측정 64

[그림. 31] Program voltage 시간을 증가한 Capacitance-Voltage (a), erase voltage -7 V 고정 후 시간을 증가한 Capacitance-Voltage (b) 65

[그림. 32] Vref 형태로 나타낸 소자의 시냅스 가중치[이미지참조] 66

[그림. 33] Pt/Cr/HfO₂/Pt/Cr/HfO₂/SiO₂/Si의 Current-Voltage 특성 곡선 66

*표시는 필수 입력사항입니다.

| 전화번호 |

|---|

| 기사명 | 저자명 | 페이지 | 원문 | 기사목차 |

|---|

| 번호 | 발행일자 | 권호명 | 제본정보 | 자료실 | 원문 | 신청 페이지 |

|---|

도서위치안내: / 서가번호:

우편복사 목록담기를 완료하였습니다.

*표시는 필수 입력사항입니다.

저장 되었습니다.