권호기사보기

| 기사명 | 저자명 | 페이지 | 원문 | 기사목차 |

|---|

결과 내 검색

동의어 포함

표제지

요약

Abstract

목차

제1장 서론 12

제2장 배경 이론 14

2.1. 클럭/데이터 복원 회로 14

2.2. 일반적인 클럭/데이터 복원 회로의 구조 16

2.3. 하프-레이트 뱅뱅 위상 검출기 19

2.4. 기준 클럭 없는 클럭/데이터 복원 회로 22

2.5. 단일 루프 클럭/데이터 복원 회로 23

제3장 주파수 획득 범위에 제한이 없는 단일 루프 연속-레이트 클럭/데이터 복원 회로 25

3.1. 제안하는 CDR의 구조 및 동작 원리 25

3.2. 뱅뱅 위상 검출기 27

3.3. FD 제어기 30

3.4. 모드 스위치 34

3.5. 주파수 검출기 37

3.6. 전하 펌프 40

3.7. 전압 제어 발진기 43

3.8. 고정 검출기 45

제4장 모의 실험 결과 및 고찰 47

4.1. 제안하는 CDR의 레이아웃 47

4.2. 제안하는 CDR의 모의 실험 결과 50

4.3. 제안하는 CDR의 성능 비교 56

제5장 결론 58

참고문헌 59

그림 2.1. 클럭/데이터 복원 회로의 기본 동작 14

그림 2.2. 데이터와 클럭의 위상 15

그림 2.3. 일반적인 클럭/데이터 복원 회로의 구조 16

그림 2.4. 위상차에 따른 위상 검출기의 출력 전압 17

그림 2.5. 일반적인 선형 위상 검출기의 구조 17

그림 2.6. 일반적인 뱅뱅 위상 검출기의 구조 18

그림 2.7. 풀-레이트와 하프-레이트의 클럭 비교 19

그림 2.8. 일반적인 하프-레이트 뱅뱅 위상 검출기의 구조 20

그림 2.9. 두 개의 하프-레이트 뱅뱅 위상 검출기의 동작 21

그림 2.10. 기준 클럭 있는 클럭/데이터 복원 회로의 구조 22

그림 2.11. 일반적인 기준 클럭 없는 이중 루프 클럭/데이터 복원 회로의 구조 23

그림 2.12. 일반적인 단일 루프 클럭/데이터 복원 회로의 구조 24

그림 3.1. 제안하는 CDR의 구조 25

그림 3.2. 네 가지 모드의 알고리즘 순서도 26

그림 3.3. (a) 첫 번째 뱅뱅 위상 검출기의 구조 (b) 첫 번째 뱅뱅 위상 검출기의 동작 28

그림 3.4. (a) 두 번째 뱅뱅 위상 검출기의 구조 (b) 두 번째 뱅뱅 위상 검출기의 동작 29

그림 3.5. FD 제어기의 블록도 30

그림 3.6. 데이터와 샘플링 지점의 타이밍도 31

그림 3.7. FUP과 FUP_EX의 타이밍도 31

그림 3.8. 카운터의 블록도 32

그림 3.9. FUP 신호의 발생 빈도 32

그림 3.10. 주파수 비에 따른 FUP과 FUP_EX 신호 33

그림 3.11. 모드 스위치의 블록도 34

그림 3.12. 모드 스위치의 동작 35

그림 3.13. 초기 출력 주파수에 따른 CDR의 모드 변화 36

그림 3.14. 제안하는 주파수 검출기의 구조 37

그림 3.15. 주파수 획득 과정의 타이밍도 38

그림 3.16. 전하펌프의 구조 41

그림 3.17. 전류 매칭 시뮬레이션 결과 42

그림 3.18. 링 전압 제어 발진기의 블록도 43

그림 3.19. 링 전압 제어 발진기의 지연 셀 44

그림 3.20. 링 전압 제어 발진기의 코너 시뮬레이션 결과 45

그림 3.21. 고정 검출기의 블록도 46

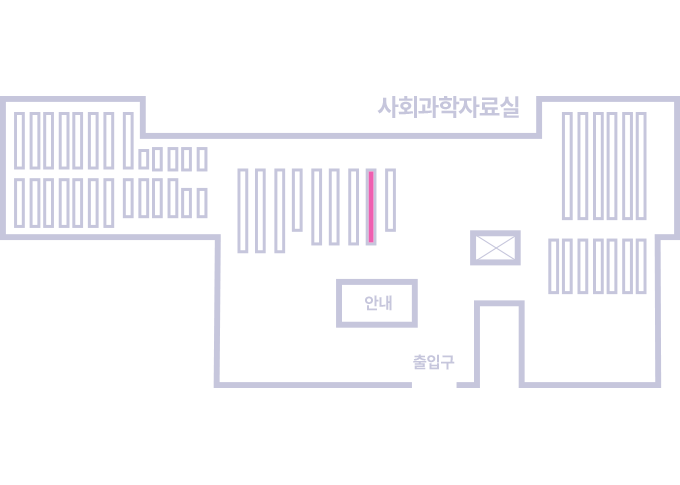

그림 4.1. 칩의 최상위 레이아웃과 핀 배치도 47

그림 4.2. 제안하는 CDR의 레이아웃 48

그림 4.3. 제안하는 위상 검출기의 레이아웃 49

그림 4.4. 제안하는 CDR의 시뮬레이션 결과 50

그림 4.5. 초기 주파수에 따른 시뮬레이션 결과 51

그림 4.6. 주파수 획득 과정의 시뮬레이션 결과 52

그림 4.7. 복원된 클럭의 아이-다이어그램 53

그림 4.8. 제안하는 CDR의 연속-레이트 시뮬레이션 54

그림 4.9. 주파수 고정 이후 제어 전압의 리플(ripple) 55

인터페이스 회로에 있어서 필요한 데이터 전송량이 증가함에 따라 고속의 데이터를 복원하는 클럭/데이터 복원회로(clock and data recovery, CDR)의 중요성이 높아지고 있다. 종래의 단일 루프 CDR은 면적과 전력소모에 강점을 가지지만, 제한적인 동작 범위와 동작 속도를 가지고 있다. 이를 해결하기 위해 본 논문에서 새로운 방식의 주파수 획득 과정을 제안한다.

제안하는 클럭/데이터 복원 회로는 단일 루프로 이루어져 있으며, 고속의 데이터를 안정적으로 복원하기 위해 하프-레이트(half-rate)에서 동작하도록 설계되었다. 데이터 정보를 샘플링하는 뱅뱅 위상검출기(bang-bang phase detector, BBPD), 샘플링 된 정보를 이용하여 주파수의 속도를 판단하는 주파수검출기(frequency detector, FD), 루프 필터(loop filter) 및 전압제어 발진기(voltage-controlled oscillator, VCO)가 단일 루프를 형성하며, 주파수의 획득 범위가 좁은 단일 루프 CDR의 단점을 개선하기 위한 FD 제어기(FD controller), 모드 스위치(mode switch) 그리고 연속-레이트 기능을 수행하도록 하는 고정검출기(lock detecor)를 제안한다.

FD 제어기는 목표 주파수가 입력 주파수보다 낮거나 높은 경우를 감지하여 FD의 동작 범위를 확장시켜 줄 뿐만 아니라, 목표 주파수를 효율적으로 획득하게 하고, 모드 스위치는 주파수 획득 단계를 총 4단계로 나누어 빠르게 목표 주파수를 찾아갈 수 있도록 한다. 그 결과 제안하는 CDR은 VCO의 동작 범위 내에서 제한 없이 주파수를 획득 할 수 있으며, 기준 클럭이 필요 없어 다양한 회로에 쉽게 적용할 수 있다.

제안하는 CDR은 Samsung 28nm CMOS 공정에서 모의실험 및 레이아웃을 진행하였다. 모의실험 결과 8Gb/s에서 26Gb/s까지의 입력 데이터의 주파수를 획득하는 것을 확인하였다. 9GHz의 초기 VCO 출력 주파수로부터 각각의 입력 데이터의 주파수를 획득하는데 걸린 시간은 각각 0.47㎲, 0.42㎲이며, 10GHz의 출력 클럭에 대하여 2.14㎰의 지터를 가진다. 또한 1.0V의 공급전압에서 21.5mW의 전력소모를 보인다.*표시는 필수 입력사항입니다.

| 전화번호 |

|---|

| 기사명 | 저자명 | 페이지 | 원문 | 기사목차 |

|---|

| 번호 | 발행일자 | 권호명 | 제본정보 | 자료실 | 원문 | 신청 페이지 |

|---|

도서위치안내: / 서가번호:

우편복사 목록담기를 완료하였습니다.

*표시는 필수 입력사항입니다.

저장 되었습니다.